Introduction to FPGA Honey Khindri, Pritam Palit, Ritu Devi SERB School – 2019, TIFR

#### **Outline of Talk**

- Introduction

- What is FPGA and how it works?

- Why FPGA?

- Specification, Architecture and Max 10 board used for the project

- Installation and Set-up

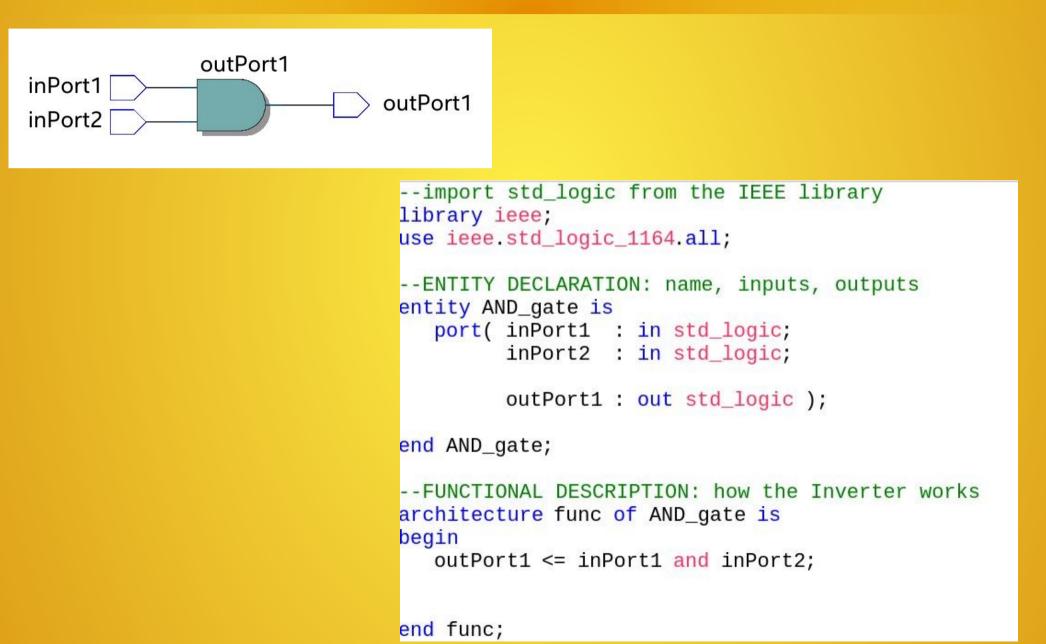

- Exercise 1 AND Gate

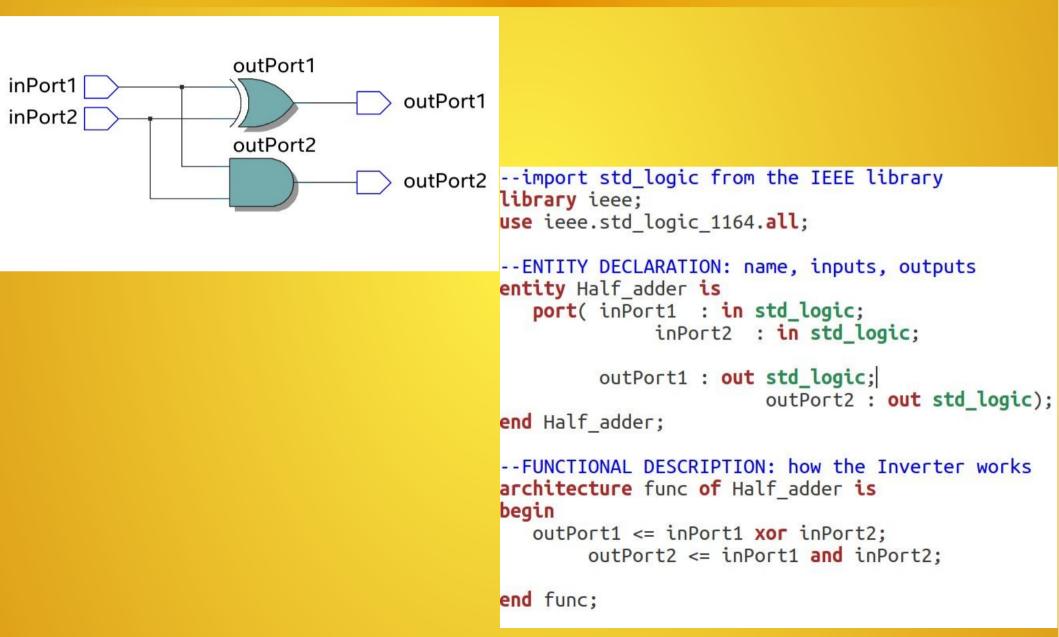

- Exercise 2 Half Adder

- Exercise 3 Hexagonal Counter

#### What is FPGA?

- FPGA is "Field Programmable Gate Array"

- Gate Array is prefabricated semiconductor device, like a silicon chip.

- FPGA, is an integrated circuit that can be configured 'in the field' by the designer to perform certain operations.

- When needed, the FPGA can be reprogrammed to perform a completely different task from its original one

### Why FPGA?

- Reconfigurable

- Small Area

- Less power consumption

- Less cost

- Speed due to parallelism

#### Parallelism - Example

#### How FPGA Works

- In FPGAs, there is no defined hardware and we are the one designing the circuit. We can configure an FPGA as we want for our purpose.

- To create a design we write Hardware Description Language (HDL), which is of two types Verilog and VHDL.

- Then the HDL is synthesized into a bit file using a BITGEN to configure the FPGA

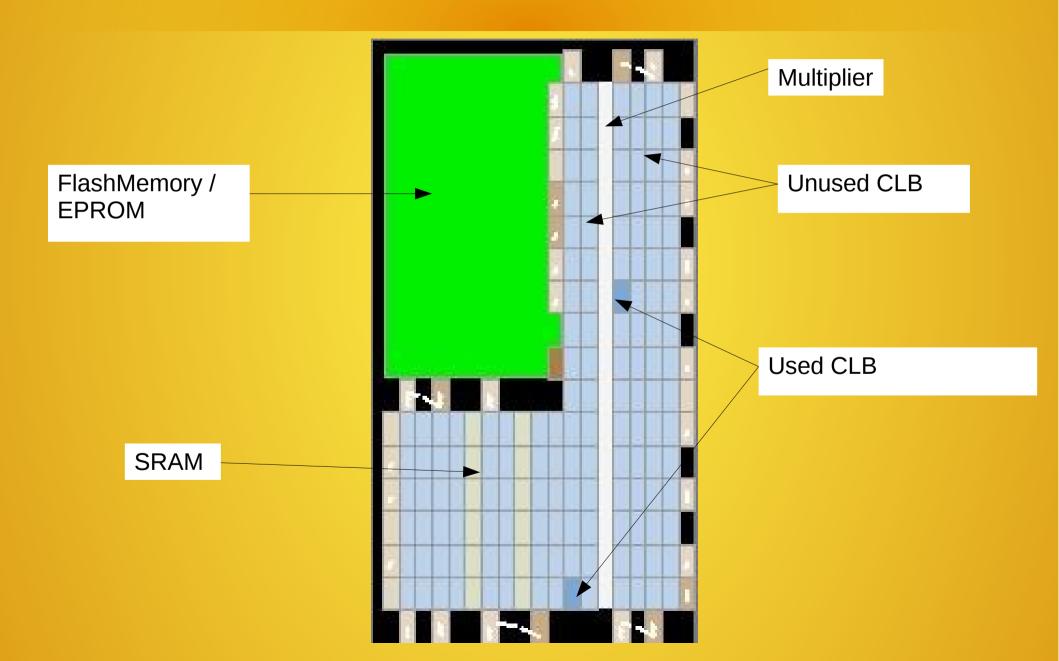

- The FPGA stores the configuration in two type of files

- .sof (Volatile memory, lost after power off) : SRAM

- .pof (Non-volatile memory) : EPROM

## Specification and programming language

- There are several FPGA vendors, e.g. Xillinx, ALTERA, Lattice etc.

- We here used ALTERA

- Altera has different families, Max10, Cyclone4, Cyclone5 etc depending on requirements.

- We used Max10, due to its low cost.

- VHDL (VHSIC Hardware description language) is used for programming the FPGA

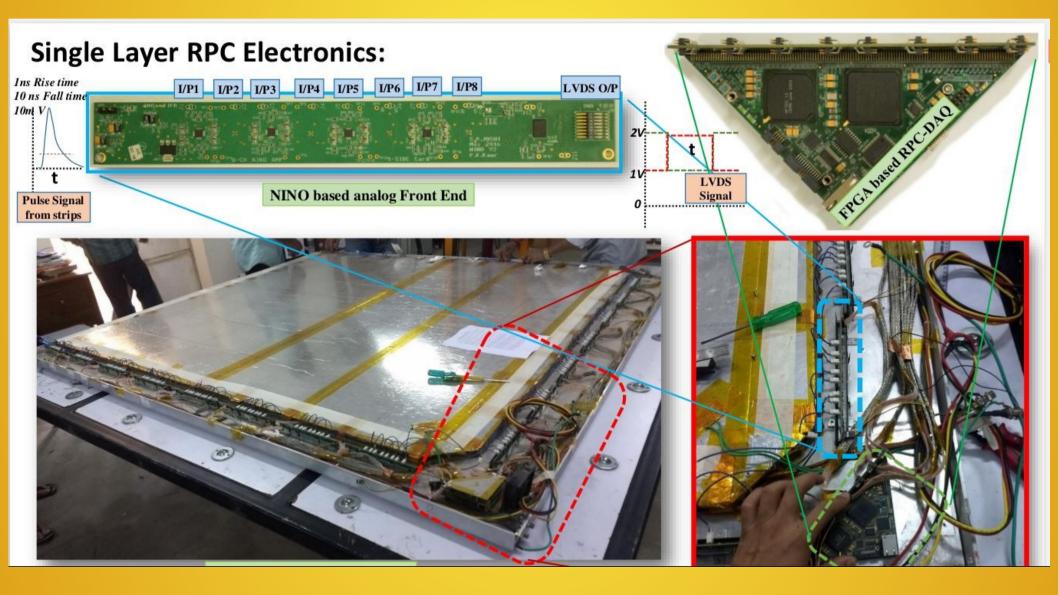

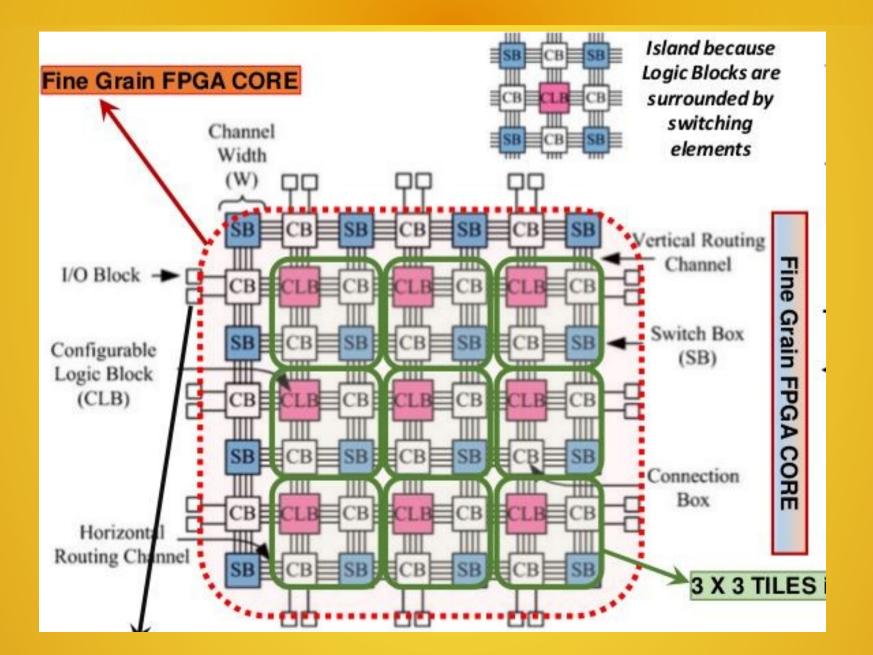

#### **FPGA** Core Structure

#### CB and SB

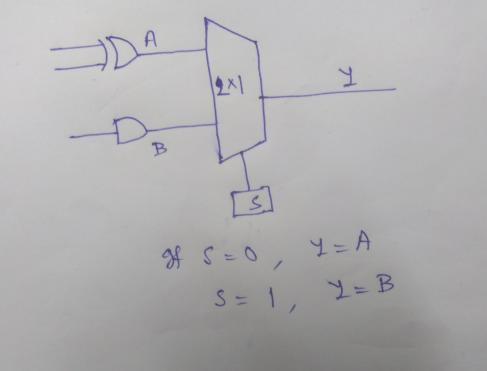

• MUX is used as a switch.

- Both CB, SB act as switch. CB can connect horizontally or vertically, while SB can do both.

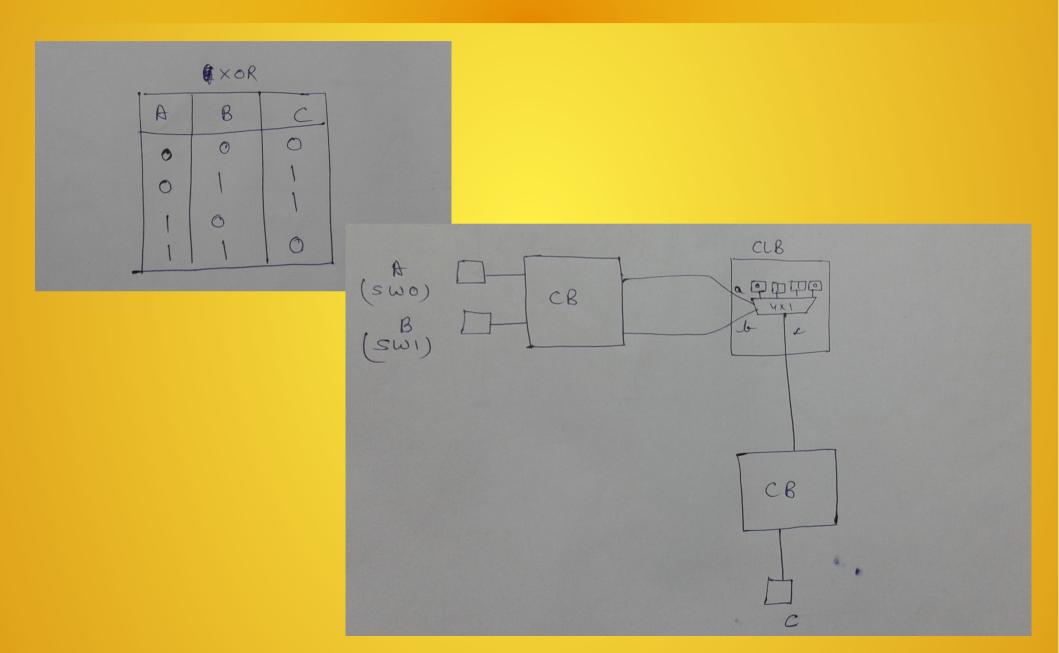

#### CLB and LUT

#### Max10 Development Board Architecture

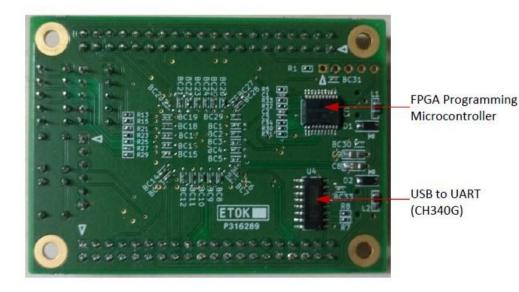

Figure 1. The Max\_10\_Dev Board Top Side

Figure 2. The Max\_10\_Dev Board bottom side

#### Software installation for the Project

- Quartus Prime (Custom Software by ALTERA)

- To compile and load the VHDL code and program the FPGA hardware accordingly

- ModelSim-Intel FPGA Edition

- To emulate , i.e. to simulate the hardware using software

- MAX 10 FPGA device support

- To create the environment of Max 10 family

#### Exercise 1 - AND

#### Exercise 2 – Half Adder

#### Memory Allocation in FPGA

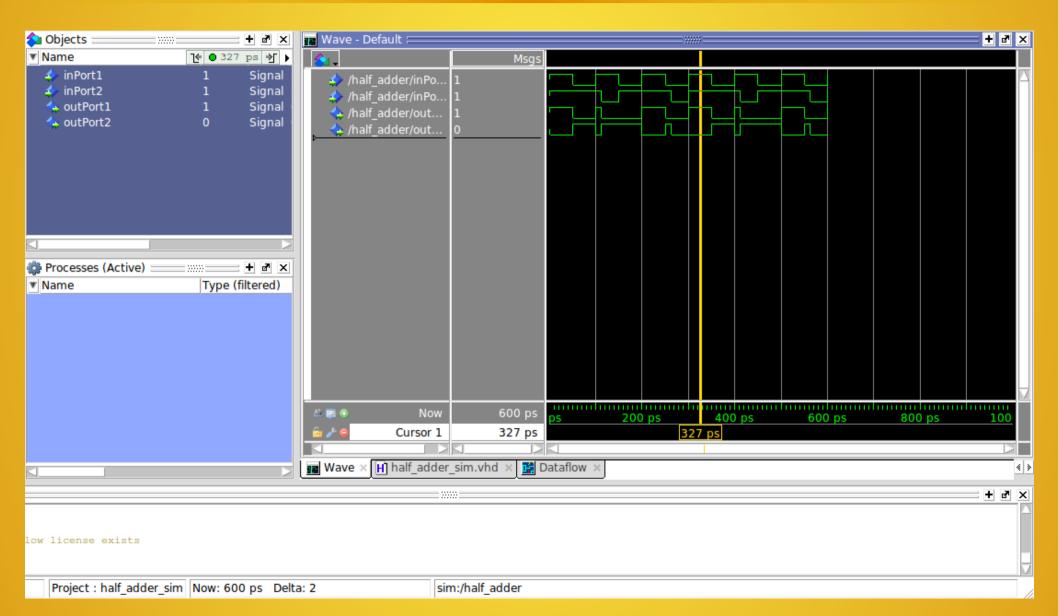

#### Emulation of Half Adder by ModelSim

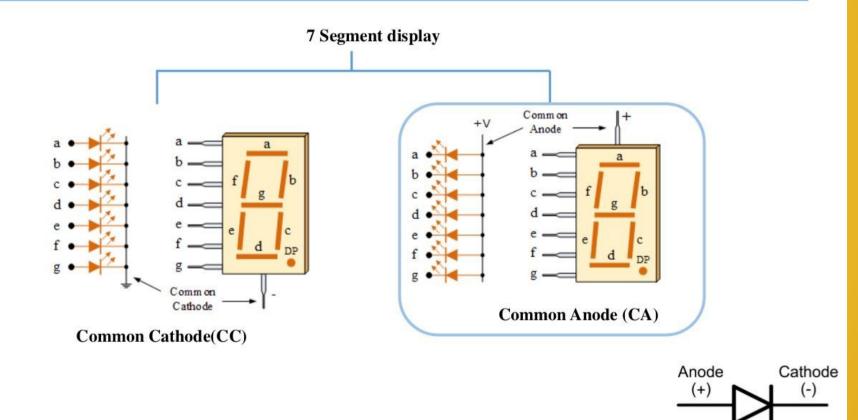

#### Hexagonal Counter – Display types

#### SEVEN SEGMENT DISPLAY TYPES

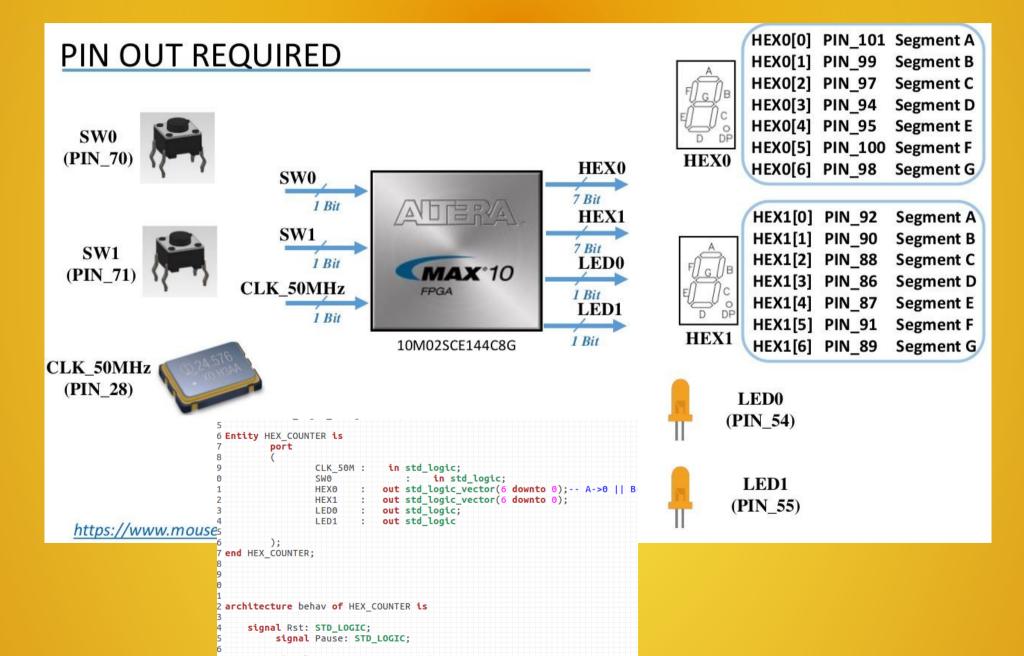

#### Exercise 3 – Hexagonal Counter

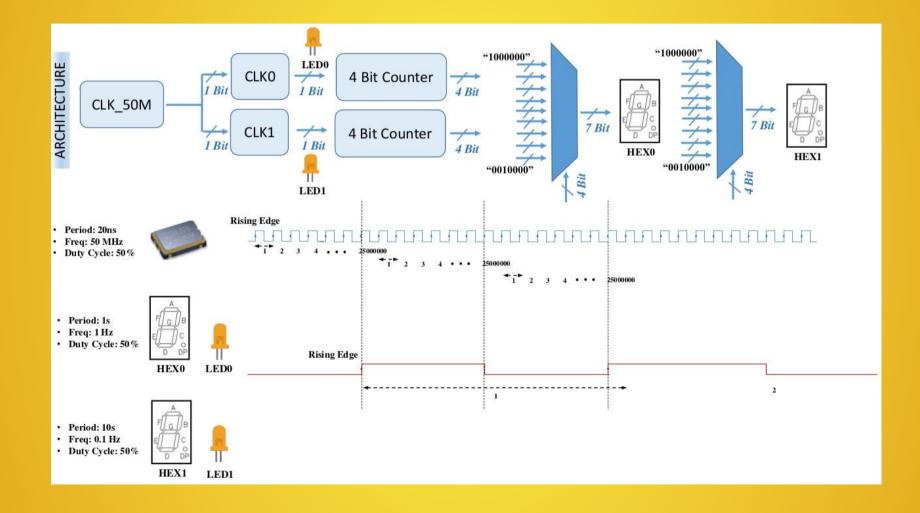

#### Hexagonal Counter Architecture

#### Hexagonal Counter Code

| HEX0 <= "1000000" | when counter0 | SHARE = "0000"              | else     |      |  |

|-------------------|---------------|-----------------------------|----------|------|--|

| "1111001" when    | counter0 SHAR | E = "0001" else             |          |      |  |

|                   |               | n counter0 SHARE            | = "0010" | else |  |

|                   | "0110000" whe | n counter0_SHARE            | = "0011" | else |  |

|                   | "0011001" whe | n counter0_SHARE            | = "0100" | else |  |

|                   |               | <pre>n counter0_SHARE</pre> |          |      |  |

|                   | "0000010" whe | <pre>n counter0_SHARE</pre> | = "0110" | else |  |

|                   |               | <pre>n counter0_SHARE</pre> |          |      |  |

|                   |               | <pre>n counter0_SHARE</pre> |          |      |  |

|                   | "0010000" whe | <pre>n counter0_SHARE</pre> | = "1001" | else |  |

| "1000000";        |               |                             |          |      |  |

|                   |               |                             | _        |      |  |

| HEX1 <= "1000000" |               |                             | else     |      |  |

| "1111001" When    |               | E = "0001" else             |          |      |  |

|                   |               | n counter1_SHARE            |          |      |  |

|                   |               | n counter1_SHARE            |          |      |  |

|                   |               | <pre>n counter1_SHARE</pre> |          |      |  |

|                   |               | <pre>n counter1_SHARE</pre> |          |      |  |

|                   |               | <pre>n counter1_SHARE</pre> |          |      |  |

|                   |               | <pre>n counter1_SHARE</pre> |          |      |  |

|                   |               | <pre>n counter1_SHARE</pre> |          |      |  |

|                   | "0010000" whe | <pre>n counter1_SHARE</pre> | = "1001" | else |  |

| "1000000";        |               |                             |          |      |  |

|                   |               |                             |          |      |  |

#### Acknowledgement

We would like to thank our project supervisor, Salam Thoithoi Singh and also the EHEP organizers for this wonderful project.

# **LPGA** FPGA everywhere. memecrunch.com

## Thank you!

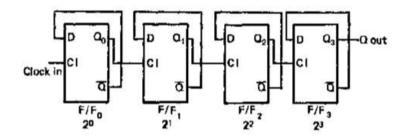

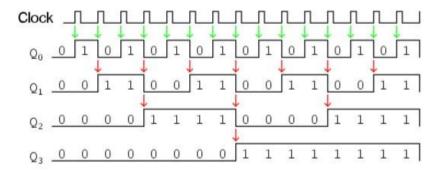

#### Hexagonal Counter

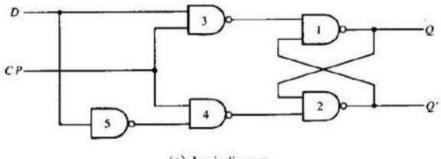

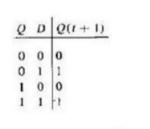

#### COUNTER USING D-FLIPFLOP

0

(b) Characteristic table (c) Characteristic equation

(d) Graphic symbol