# Progress of G-APD (SiPM) based Imaging Camera for ACT

(S.S.Upadhya, on behalf of HAGAR group, TIFR, Mumbai)

- Introduction

- Camera specifications

- Challenges faced

- Design & Development (Front End & Back end)

- Status & Results

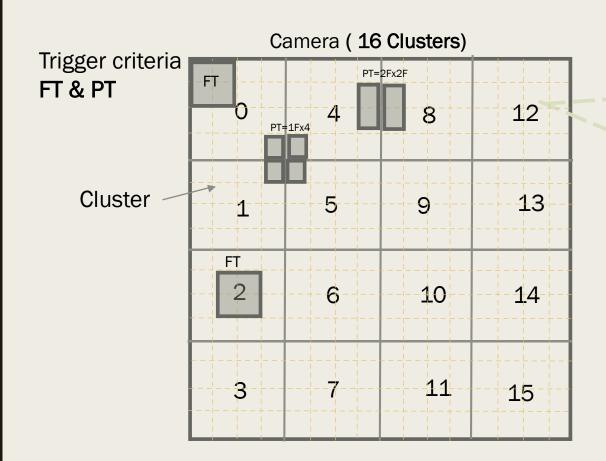

# **Camera Specifications**

- Imaging camera housed at focal point of 4m telescope

- Operational site is Hanle.

- Temp variation of 10°C over a night and Avg night temp varies -20°C to +20°C over the year

- Observation condition : Dark to Bright night sky regions or Twilight condition

- 256 pixels Camera

- FOV 5°x5° (353x353mm)

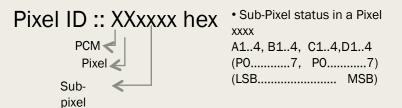

- Pixel Size 0.31° (22.1x22.1mm)

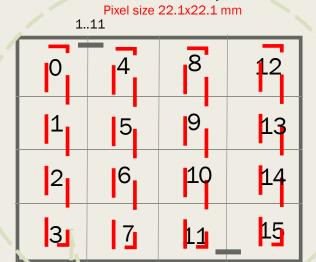

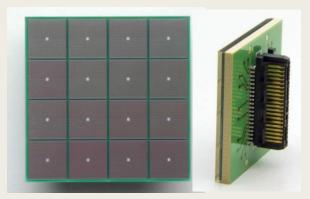

- Pixel Sensor S13361: G-APD(SiPM) of 4x4 array (13x13mm), Sub-pixel of 3x3mm size

- Detection of Cerenkov flashes (~5ns) of few 10s of pe against large NSB back ground(93Mpe/s per pixel)

- Pixel information to be recorded

- Pulse profile@1GSPS or Charge

- Dynamic range up to 1000pe/pixel with a resolution of 0.5 pe (up to 10pe)

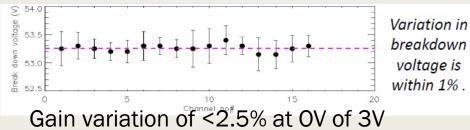

- In-situ calibration of pixel gain of Camera and gain stability monitoring

- Trigger criteria: 4 near neighbor pixels crossing set pe threshold and rate is Few tens of Hz

# Challenges faced

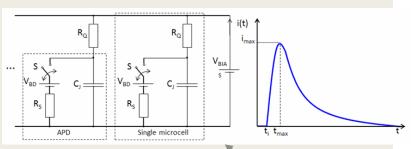

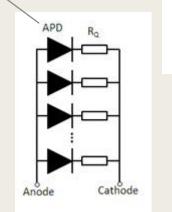

- Due to limitation of light concentrator, sensor area could not be optimized less than 12mm² and 4x4 array SiPM used. Due to large decay of SiPM pulses, individual 16 sub pixel pulses are processed & added in electronics for better S/N ratio

- The detection of faint Cerenkov photon shower of 10s of photons in few nano-seconds window against continuous huge night sky photons of 93Mpe per second per pixel during dark night observation, which increases further in observations under bright sky region or moon lit condition.

- The physics need of wide dynamic range from single photon to 1000 photons per pixel.

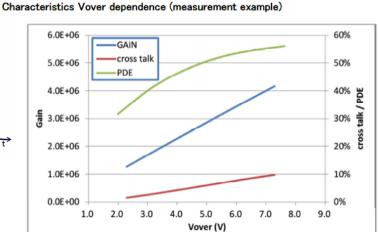

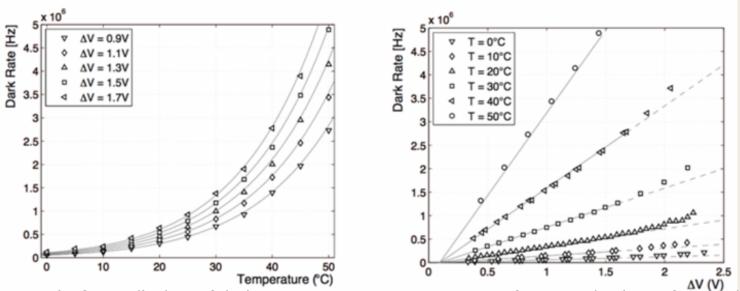

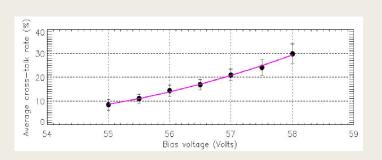

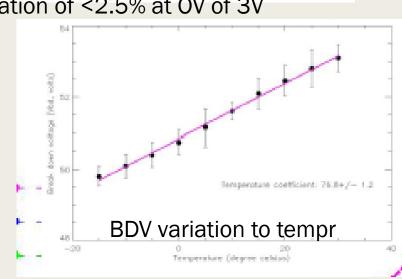

- Extreme night temperature of +30°C to -25°C in the site Hanle(4300m Altitude), Ladakh where the Camera is planned to be deployed. SiPM gain is sensitive to temperature and hence Bias voltage is need to be compensated continuously by monitoring temperature near SiPM (G-APD)

- Space constraints of front end electronics (< 22.1mm width PCB needs to accommodate 16 subpixel fast analog signal conditioning electronics) demands choice of SMD component design with 10 or more layers PCB. This miniaturization makes PCB population (soldering) very challenging during in-house prototype development.

- High data through-put due to Giga sampling of the pulse profile

- In-situ gain calibration and monitoring

- Due to space constraint and complexity of the design, FPGA and microcontroller are chosen. This demanded self up-gradation of staff skill to these new technological designs from the conventional discrete logic design.

### Pixel view of Camera(256 pixels)

### A cluster of 16 pixels

B-4

A-4

C-4

D-4

Hammatsu **\$13361-3050AS-04**

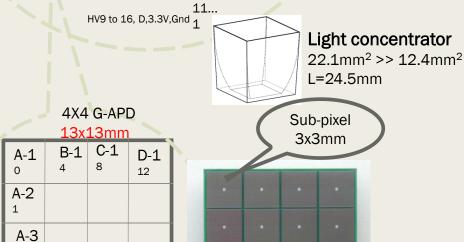

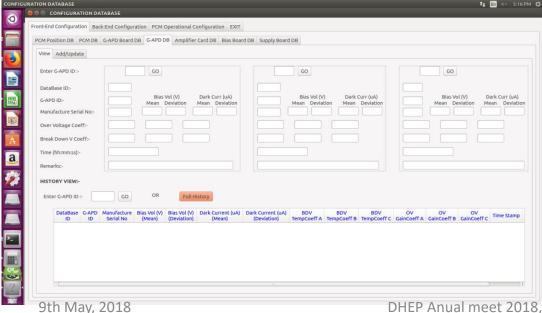

# Pixel Sensor: 4x4 GAPD (Hamamatsu S13361-3050AS-04)

13x13mm – 4x4 array, <u>74% Fill Factor</u> **Sub pixel Specifications**

- Sub-pixel: 3584 micro-cells of 50 μm pitch

- Low voltage (Vop=56V Typ.) operation

- High gain: 10<sup>5</sup> to 10<sup>6</sup>

- Operating temp -20 to +60C

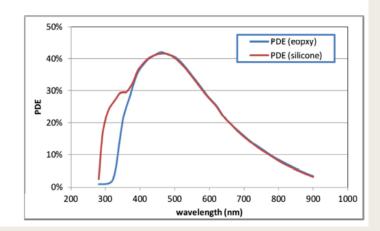

- Spectral Response 270 to 900nm Peak at 450

- PDE 40% at 450nm

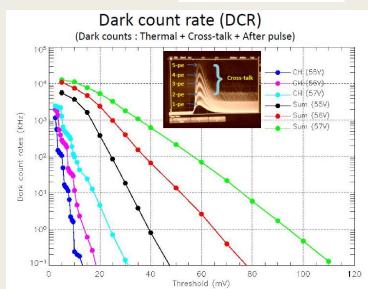

- Dark count per Sub pixel typ 0.5M Hz at 25C

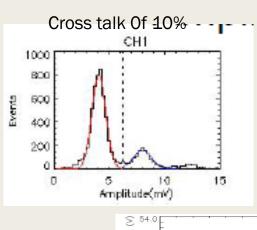

- Cross talk 3%

- Temp coeff of BD voltage is 52mV/C

Photon detection efficiency vs. wavelength (measurement example)

Pixel 4x4 array (OV=Vbias-Vbr)

- Common Bias: Gain variation of 1.25% @ 3V OV

- Gain variation of 1.5% per C

- Dark counts of 0.5 x16 = 8MHz, temperature dependent

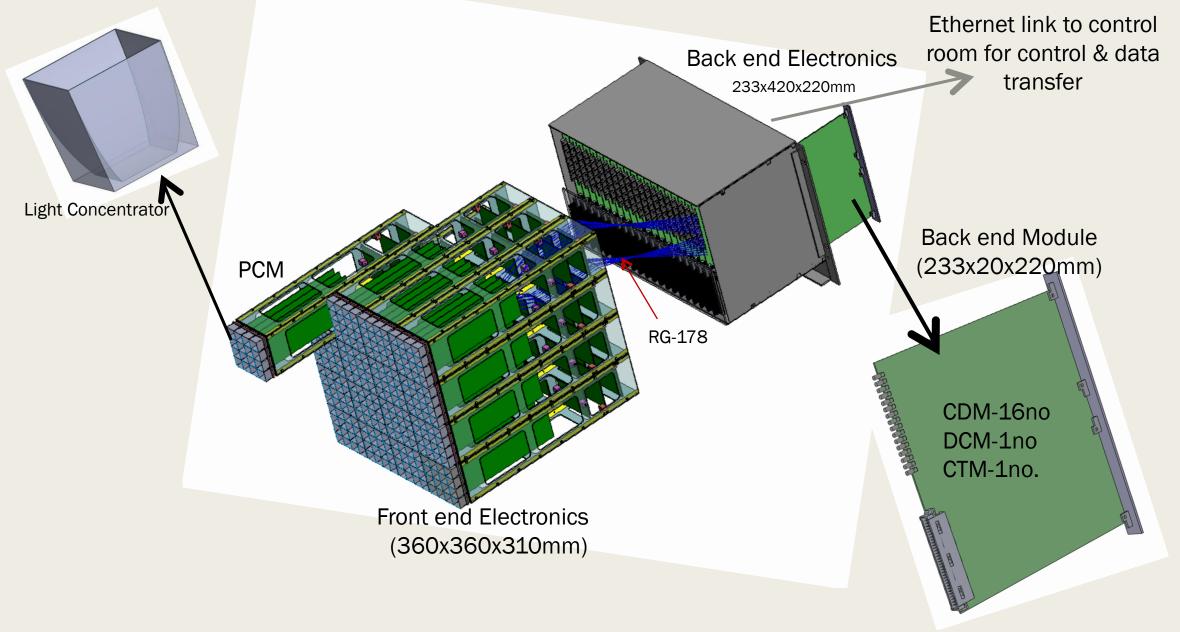

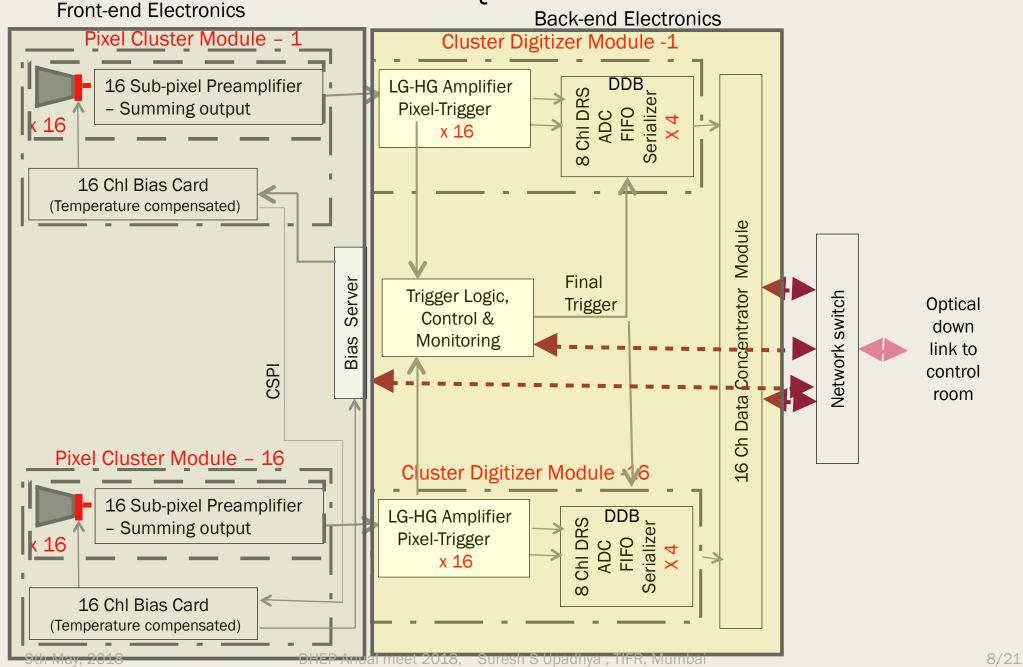

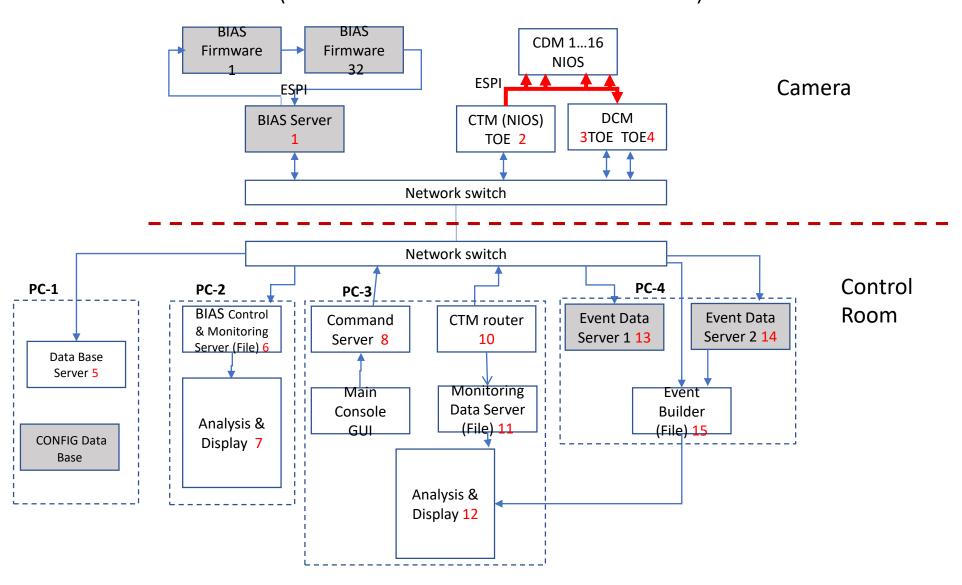

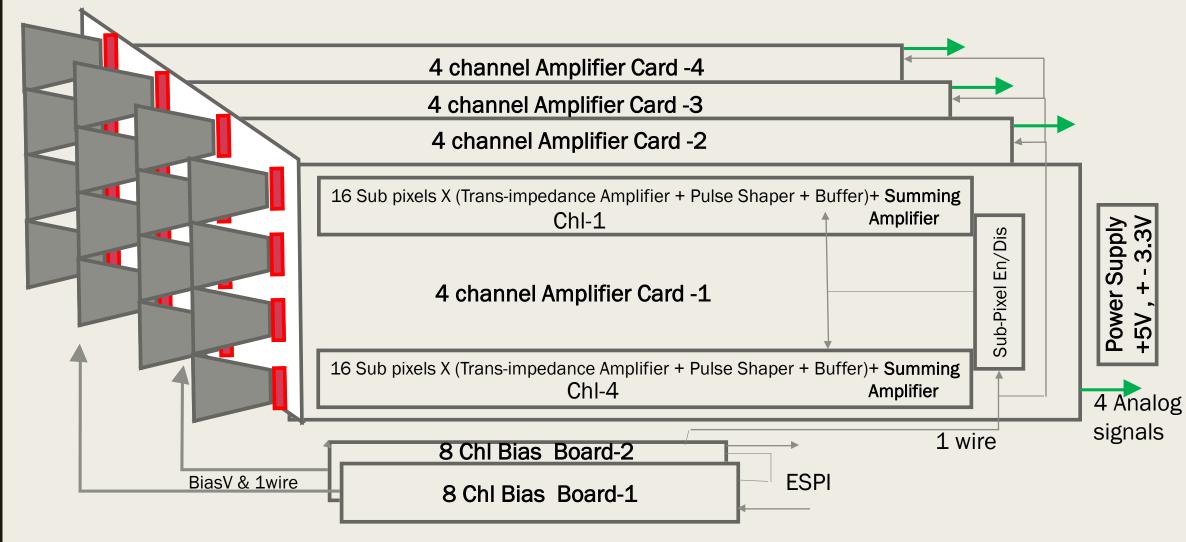

# Imaging Camera Electronics in focal plane of telescope

### CAMERA DAQ ELECTRONICS

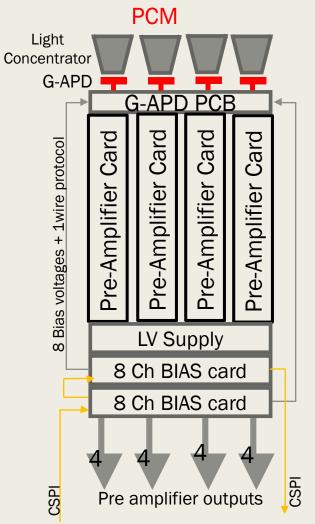

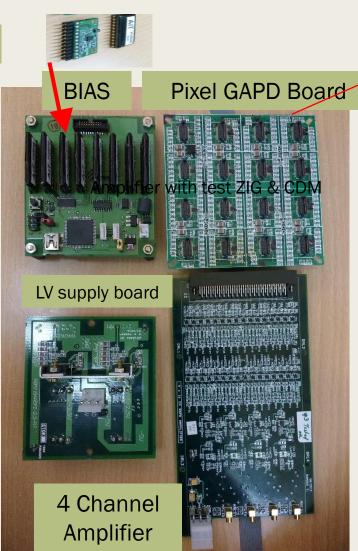

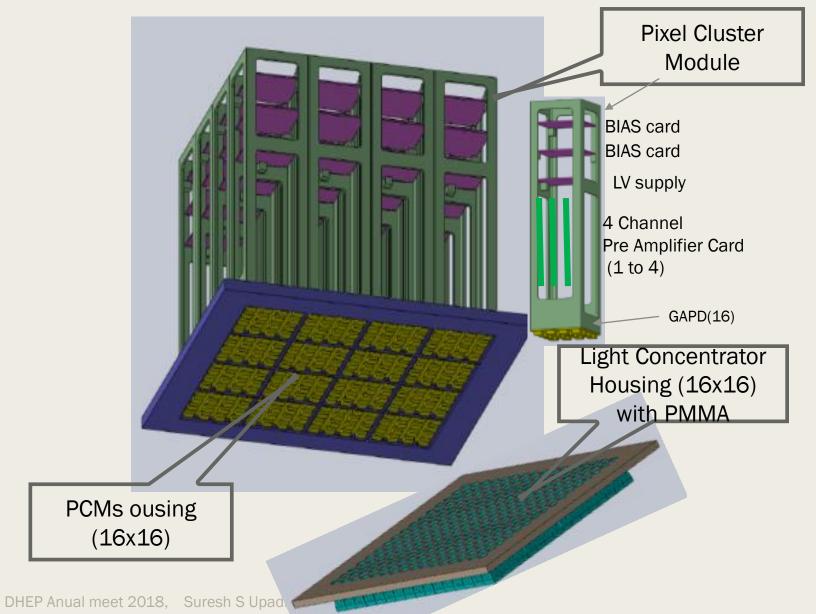

# **Pixel Cluster Module Components**

- Pixels Cluster Module(PCM) -16no.s

- Hollow Light concentrator- 16 no.s

- Square Entry(22.1mm) & Exit(12.4mm), H=25.5mm

- Concentrates pixel light onto G-APD

- GAPD PCB 1no.

- Houses 16 pluggable G-APDs (4x4 sub pixels)

- Two temperature sensors

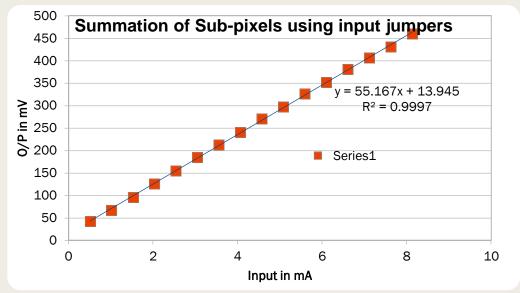

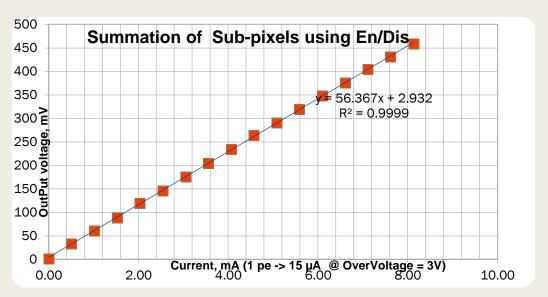

- **Pre-Amplifier Card** 4no.s

- Has 4 Pixel channels. Each Channel processes 16 sub-pixel signals

- 16 sub pixel pulses are amplified(Transimpedance), shaped and summed to get a pixel signal output

- Each Sub pixel can be Enabled/Disabled in all 4 pixels using 1-wire protocol.

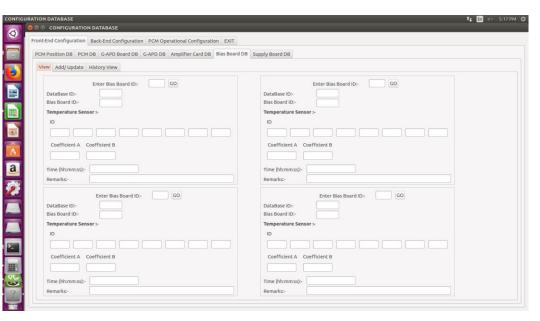

- Bias Card-2no.s

- 8 channel, 0 to 70V Bias voltage, 2.5/4mA

- Micro-controller based control & monitoring

- G-APD gain Compensated for Temperature & load variation

- 1 wire connectivity to Temperature sensors and Sub pixel selection

- CSPI link to Raspberry Pi based Bias server for overall control & monitoring of 32 Bias cards in 16 PCMs

- Raspberry Pi has Ethernet down link to remote server in control room

- LV Supply

- Caters required voltages to all the cards in a PCM

# Pixel Cluster Module

Amplifier with test ZIG & CDM

One PCM is ready for rigorous tests

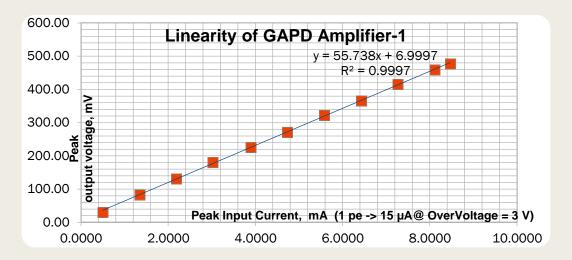

# Pixel Amplifier PG test result (Version 2)

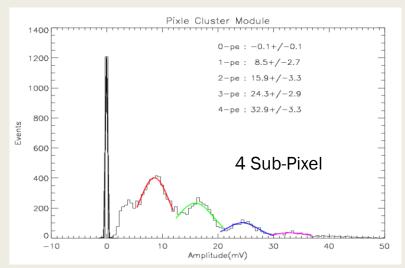

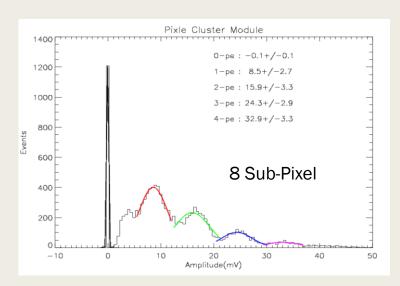

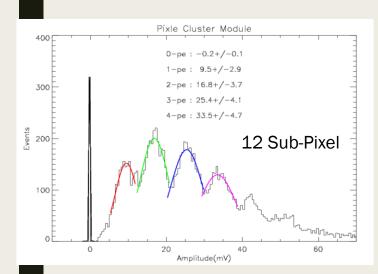

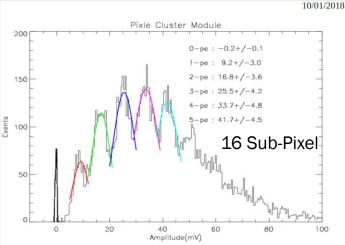

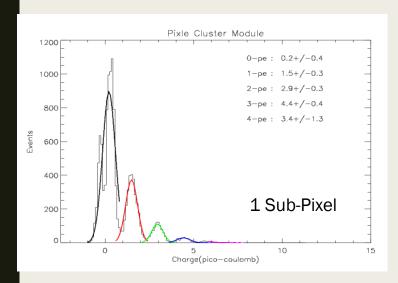

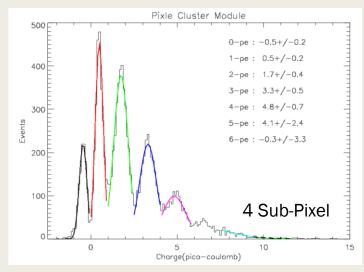

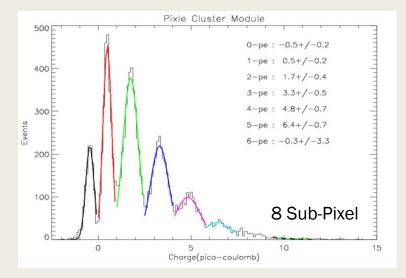

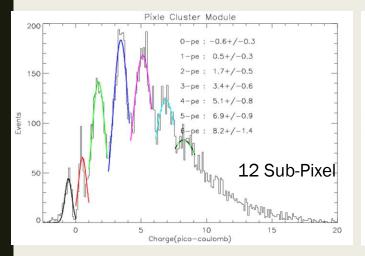

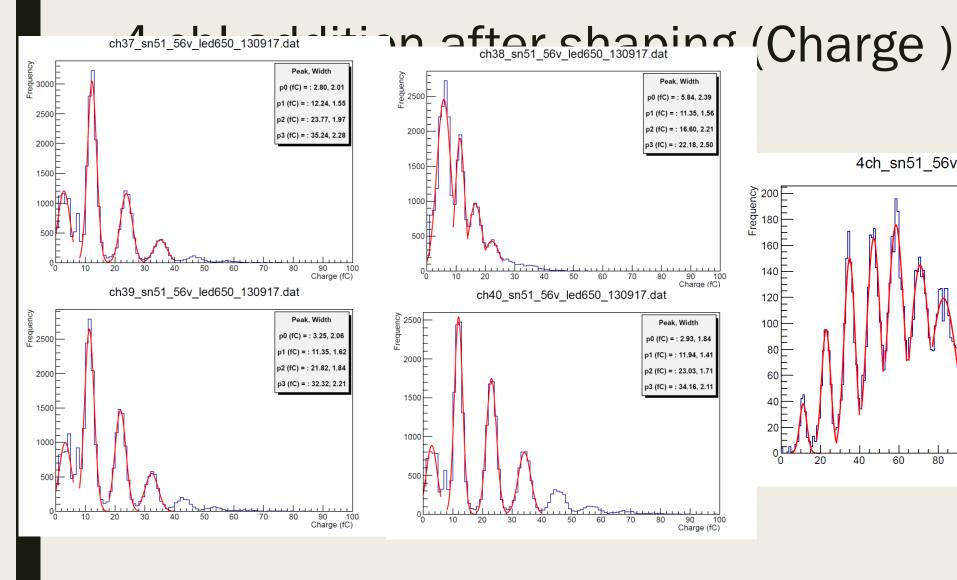

### Summation results using GAPD exposed to <u>LED flasher (Amplitude spectrum)</u>

| N<br>SubP | PtoP Amplitu |     |     |     | Average | StdDev   |          |

|-----------|--------------|-----|-----|-----|---------|----------|----------|

| 1         | 9            |     |     |     |         |          |          |

| 4         | 8.6          | 7.4 | 8.4 |     |         | 8.133333 | 0.64291  |

| 8         |              |     |     |     |         |          |          |

| 12        | 9.7          | 7.3 | 8.6 | 8.1 | 0       | 8        | 0.655744 |

| 16        | 9.4          | 7.6 | 8.7 | 8.2 | 8       | 8.125    | 0.550757 |

|           |              |     |     |     |         | 8.13333  | 0.64291  |

|           |              |     |     |     | AVerg   | 8.086111 | 0.61647  |

|           |              |     |     |     | StDev   | 0.07469  | 0.05727  |

|           |              |     |     |     |         |          |          |

### Summation results using GAPD with LED flasher (Charge )

| N<br>SubP | PtoP Charg | ďΔ  |     |     |     |     | AVerage  | Std. Dev |

|-----------|------------|-----|-----|-----|-----|-----|----------|----------|

| Subr      | rtor Charg | 30  |     |     |     |     | Average  | Sta. Dev |

| 1         | 1.3        | 1.4 | 1.5 |     |     |     | 1.45     | 0.1      |

| 4         | 1          | 1.2 | 1.6 | 1.5 |     |     | 1.433333 | 0.275379 |

| 8         | 1          | 1.2 | 1.6 | 1.5 |     |     | 1.433333 | 0.275379 |

| 12        | 1.1        | 1.2 | 1.7 | 1.7 | 1.8 |     | 1.6      | 0.324037 |

| 16        |            |     | 1.7 | 1.9 | 1.7 | 1.6 | 1.68     | 0.132665 |

|           |            |     |     |     |     | AVG | 1.519333 |          |

|           |            |     |     |     |     | SD  | 0.11393  |          |

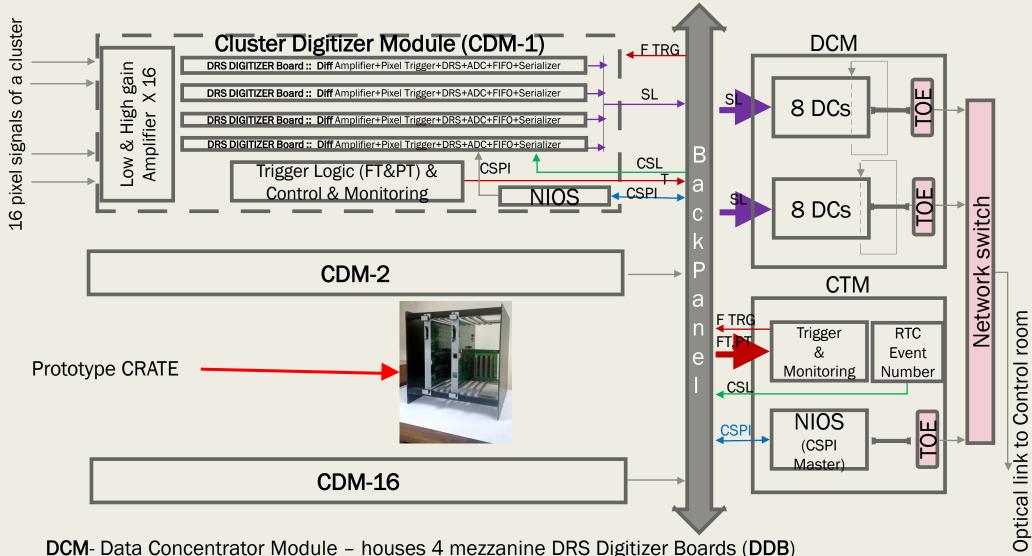

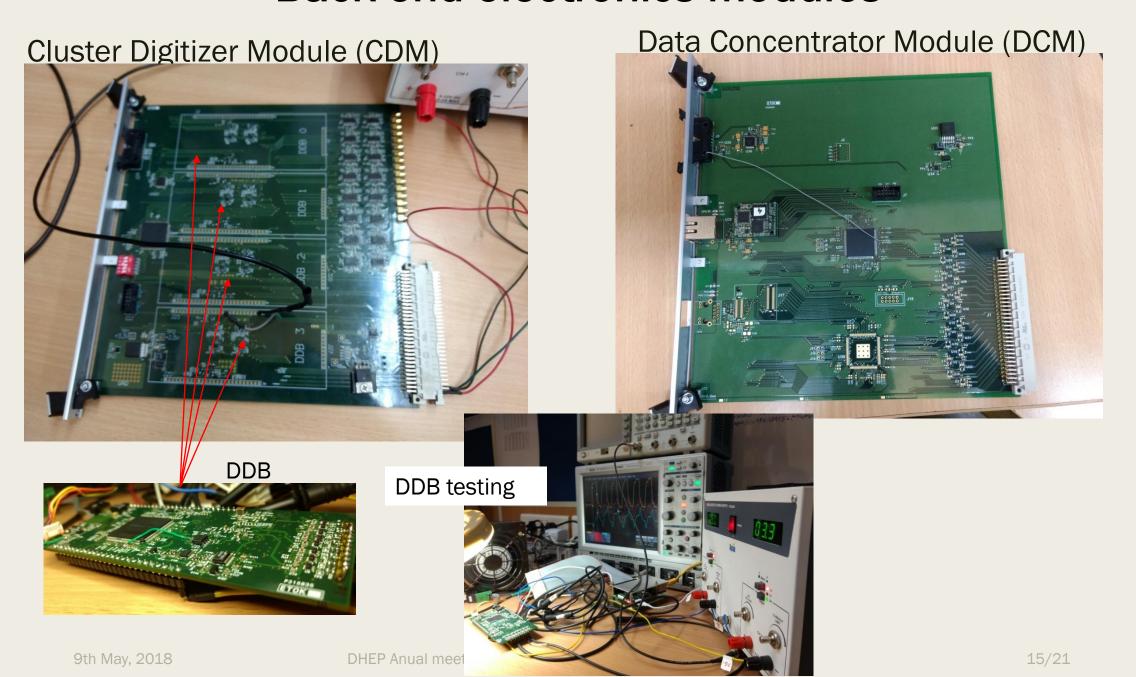

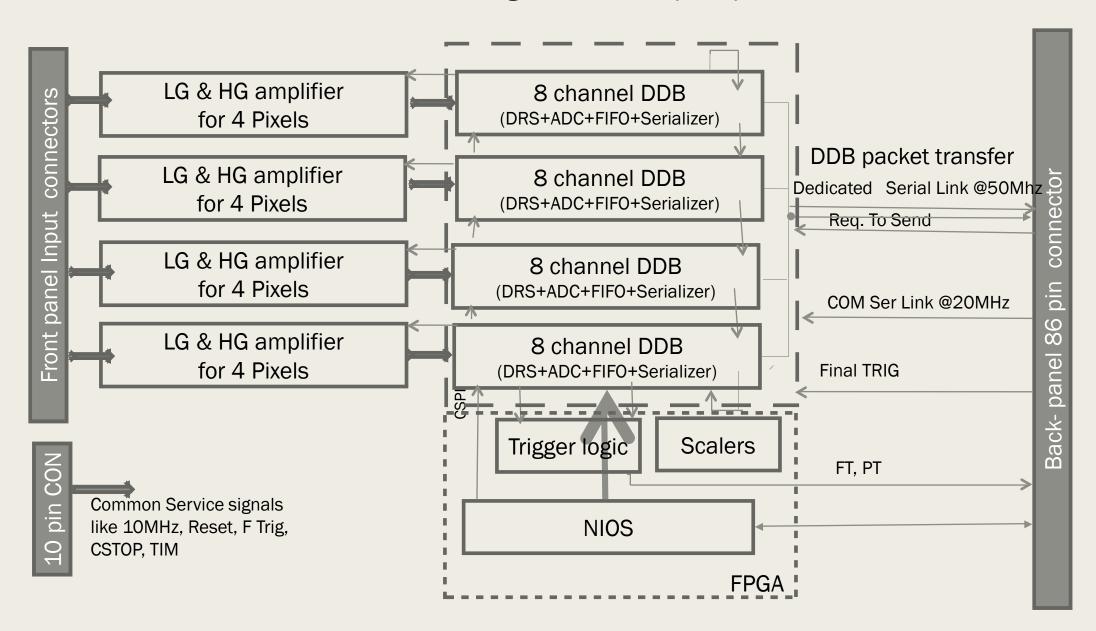

# Back end Data Electronics (Processing & Data Acquisition )

**DCM**- Data Concentrator Module – houses 4 mezzanine DRS Digitizer Boards (**DDB**)

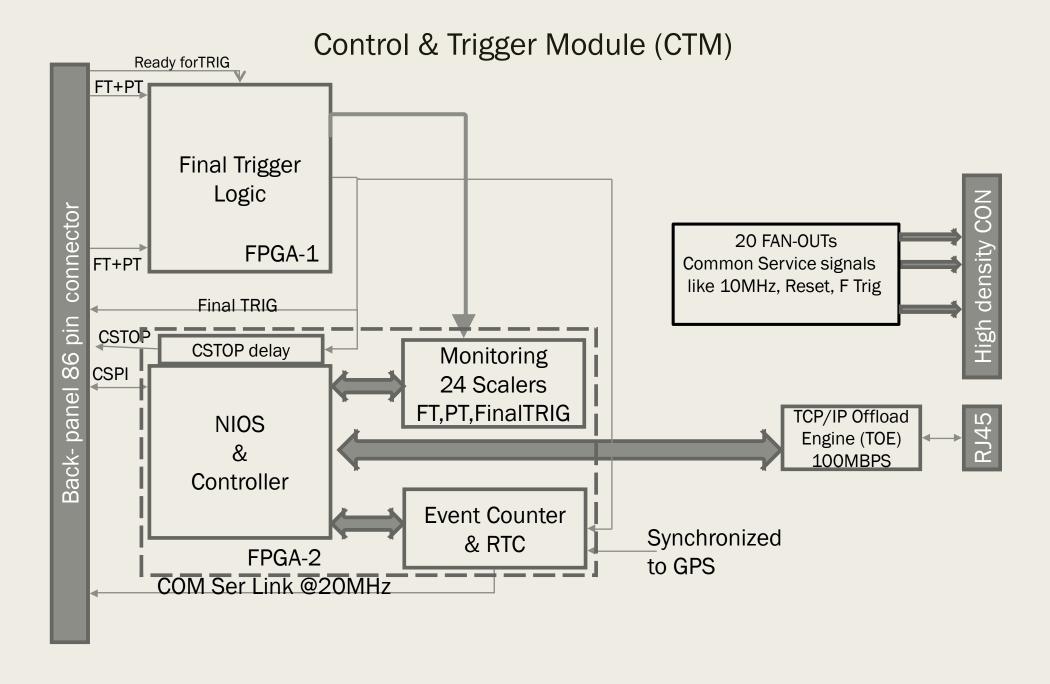

**CTM**- Control & Trigger Module

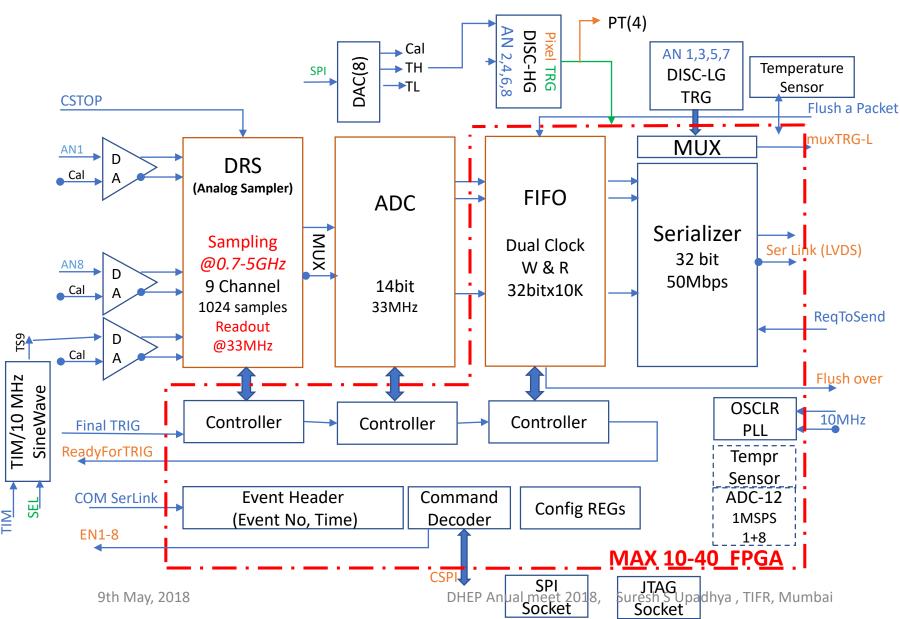

DRS- 9 chl, 1024 switched capacitor array (analog sampler), 1GSPS, ROI is muxed at Output

# Back-end electronics modules

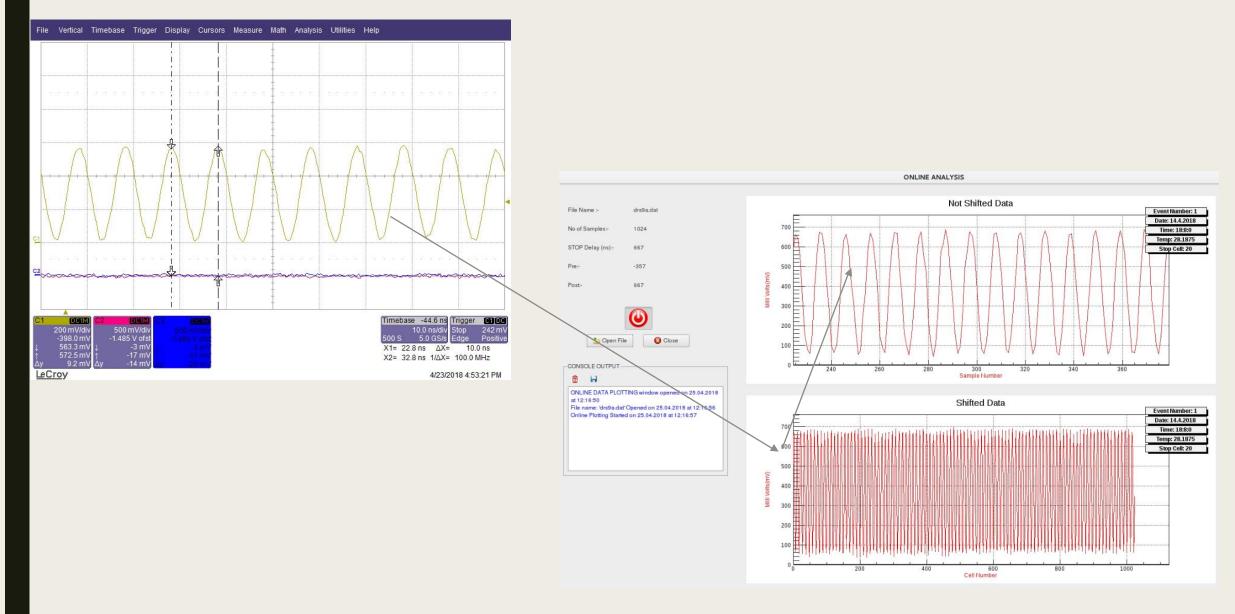

# DDB result- Sine wave sampled @1GSPS

### Customized SPI transfer protocol between Hardware modules

- A customized SPI protocol designed for communication between various modules under Single Master and One or More Slaves scheme. There are basically 3 applications

- 1. Raspberry-Pi as Master to control all 32 Bias-boards as slaves

- Master and Slave are SW controlled

- Interface signals :: MOSI,MISO(slave controlled), CLK, nSS, nBSY(optional)

- nSS invokes Slave interrupt and nSS is active for a complete data transfer cycle. Common or selective slave access.

- Byte transfer control: Fixed delay of slave latency or nBSY handshake

- 2. CTM to CDMs or other modules over back panel CSPI interface

- Master and Slave are SW controlled

- Interface signals: MOSI,MISO(slave controlled), CLK, nSS, nBSY

- nSS invokes Slave interrupt and nSS is active for complete transfer. Common or selective slave access.

- Byte transfer control by nBSY signal hand-shake

- While nSS is inactive, nBSY pulse acts as alert from any slave to Master by invoking interrupt. Master can identify the alerted slaves by issuing common command.

- 3. CDM to 4 DDBs : Single slave access

- Master is SW controlled and Slave is HW module

- Interface signals: MOSI,MISO, CLK, nSS and nSS is active for a complete transfer

# Trigger, Data throughput and Data Size

### > Trigger logic

- ✓ Pixel trigger : Pulse crossing set threshold (programmable)

- ✓ Full (4 Nearest Neighbours) / Partial (boundary triggers) Triggers in CDM.

- ✓ Partial Triggers across the Pixel Cluster Modules are resolved in CTM

### > Trigger rate

- ✓ Sampling speed @1GSPS, Region of Interest (ROI) is 100ns

- ✓ Digitization speed 33 MHz, 14-bit data,

- $\circ$  Dead time per DDB (4-pixel) 100x30nsx9chl = 27μS+3μS = 30μS, Burst Trigger rate of 33 KHz

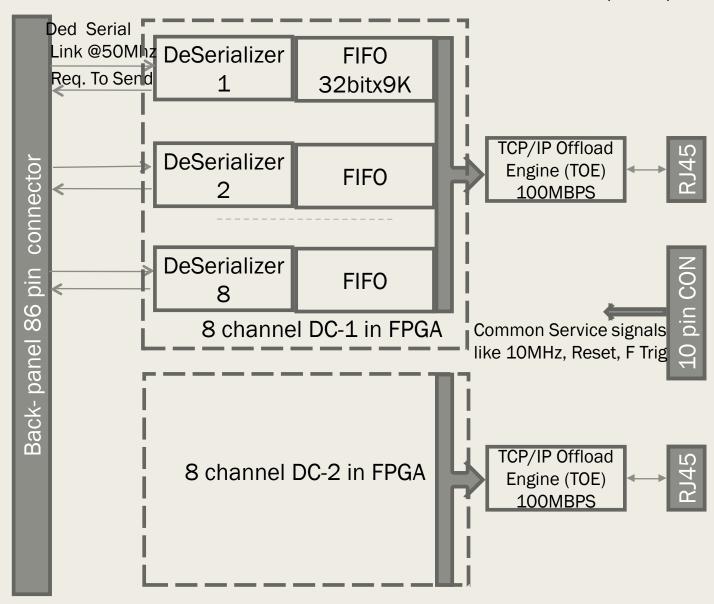

- CDMs to DCM data transfer @ 50 Mbps over 16 dedicated serial LVDS links and pushed to remote data server over two Ethernet links @ 80MBps

- Event size: 1Mb for ROI of 100ns, Sustained Trigger rate is 800Hz with a data through put of 80MBps

- Data Size for a trigger rate of 50 Hz and Pulse profile of 100ns is 22.5 GB/Hour

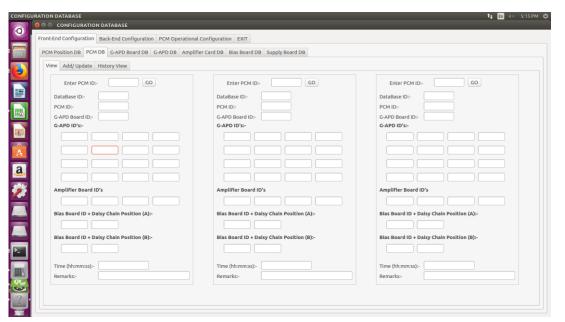

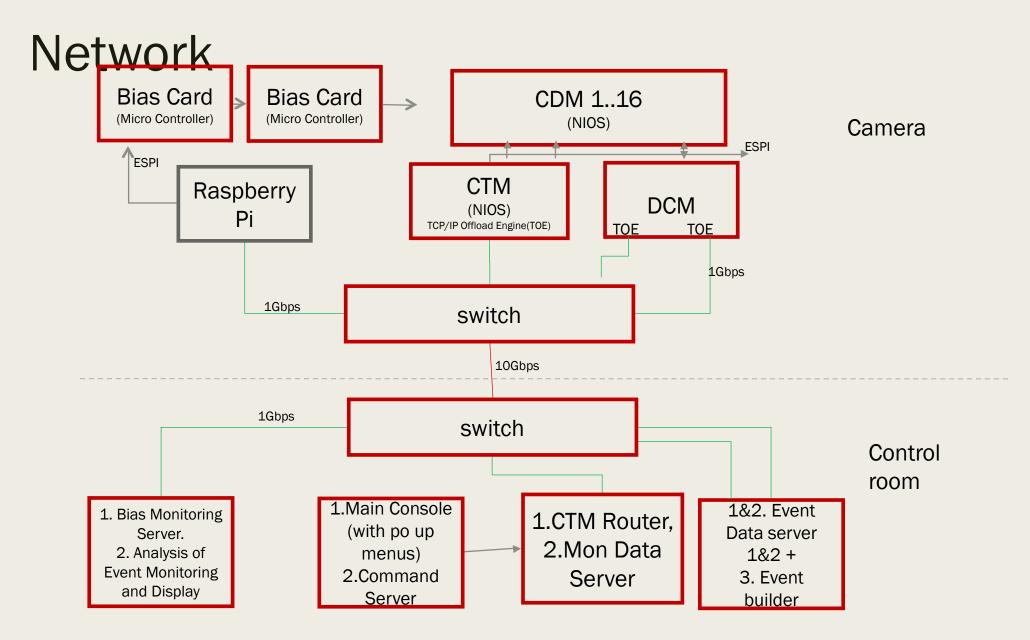

# Software Concept (Data & communication network)

### Software status – Configuration data base (Create/Update/View/History)

### Software under development

- **Event Data Server**

- **Event Builder**

# Thank you

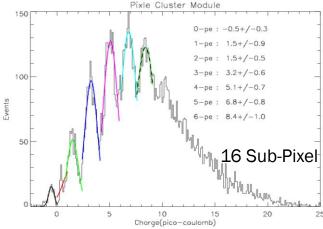

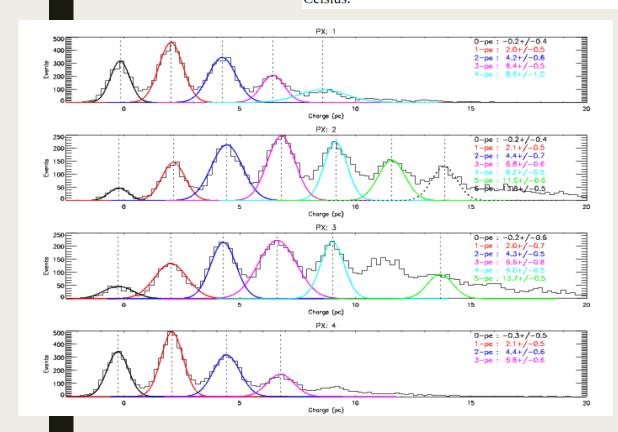

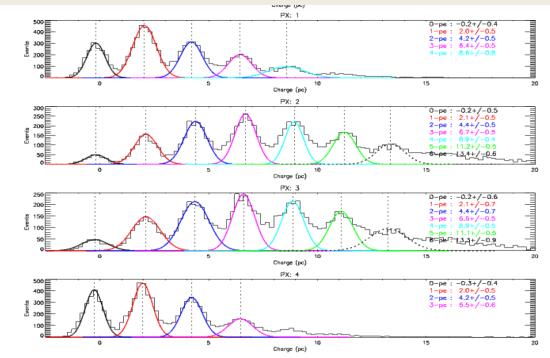

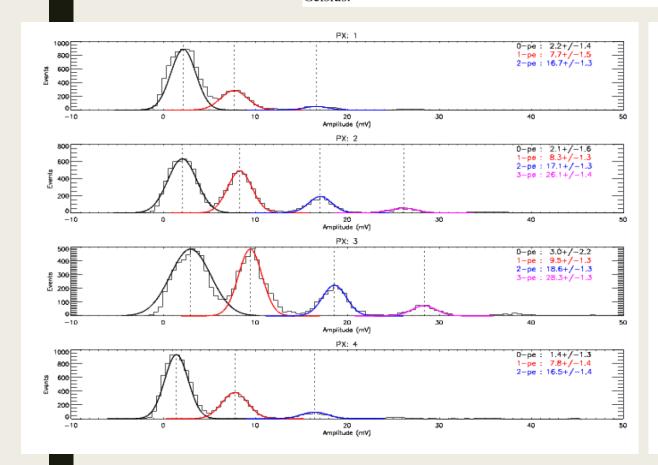

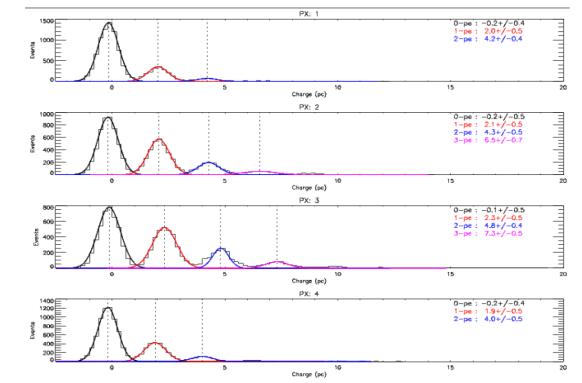

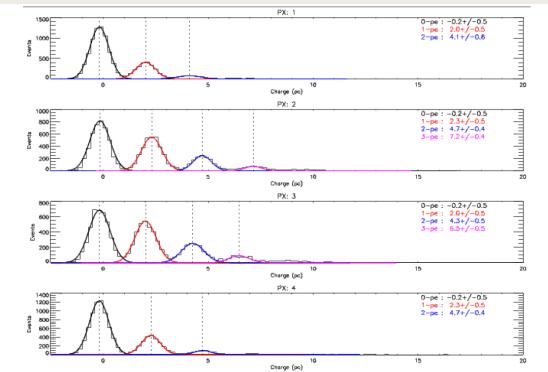

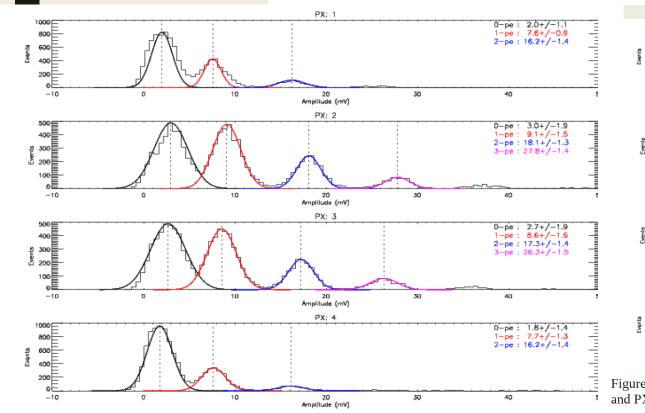

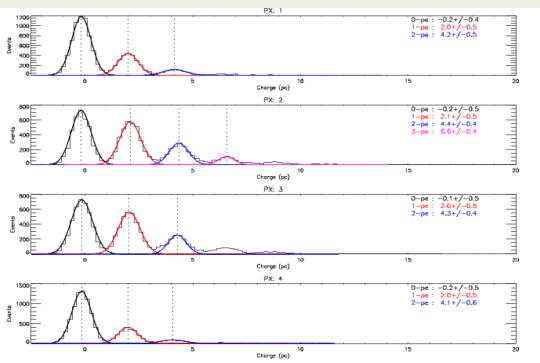

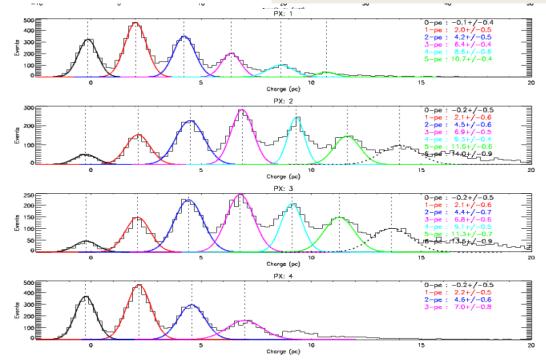

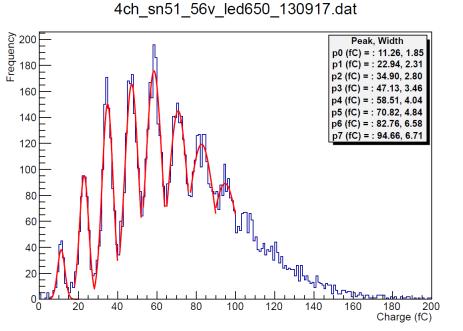

Figure-8: Pulse charge distribution of 4-subpixels (added) (configured as 1428 upper panel and 8481 lower panel). PX1, PX2, PX3 and PX4 refer to four GAPDs (g1,g2,g3,g4) used in PCM.

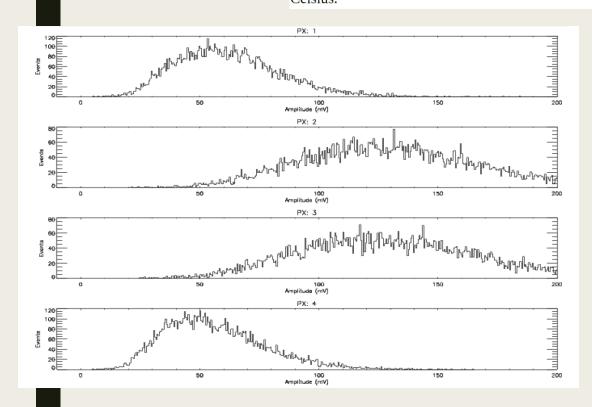

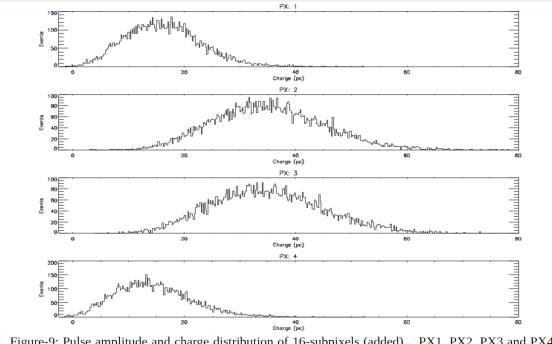

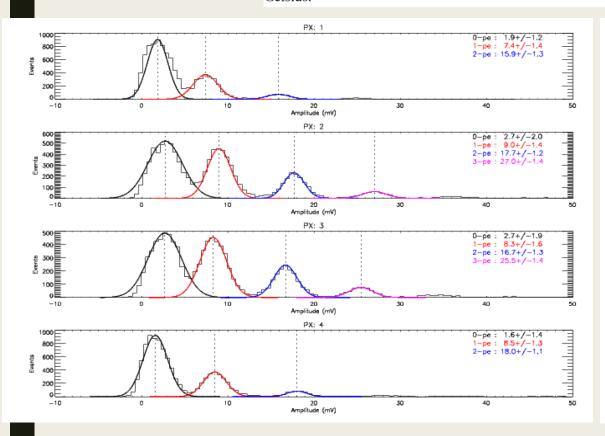

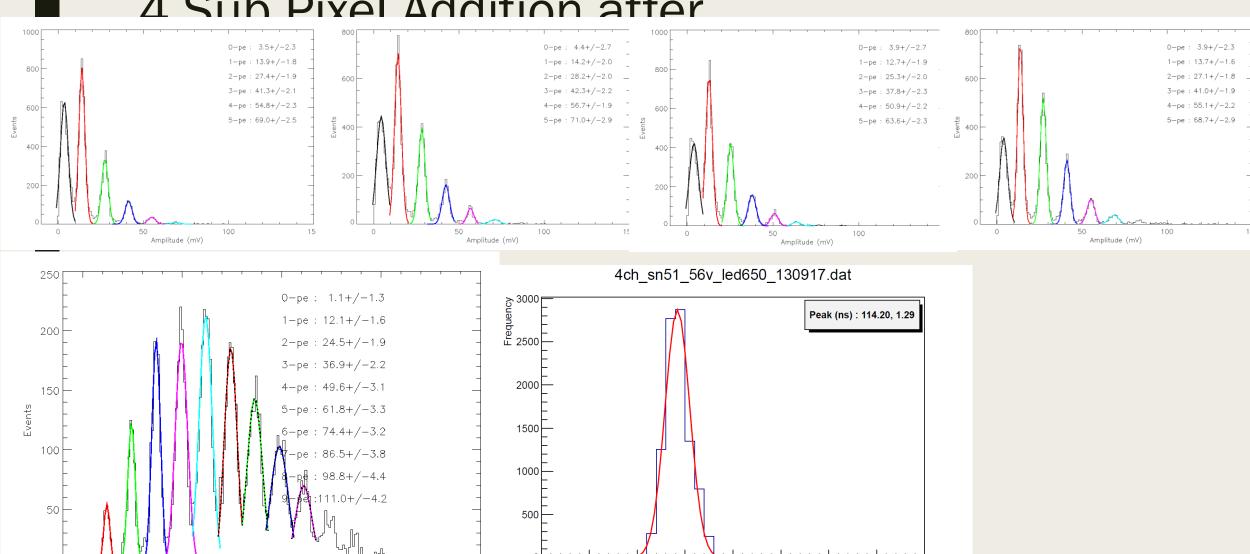

Figure-9: Pulse amplitude and charge distribution of 16-subpixels (added) . PX1, PX2, PX3 and PX4 refer to four GAPDs (g1,g2,g3,g4) used in PCM.

### General protocol for CSPI

- CSPI -serial protocol is used for communication & data transfer between HW modules in the system

- Single Master single/multiple Slaves configuration used

- nSS -Invoke interrupt in Slave to initiate the Packet transfer

- First byte is sent after a Slave interrupt latency and Byte transfer with pre defined gap or handshake

- Time out need to be implemented in both Master and Slave

- High priority Commands can be executable immediately or may be executed later in back ground. One can check for command response before reading the result

#### Packet Identifier:

bb=00 Individual Slave command

bb+C+A+W/r+Bytes(3)

bb=10 Broad cast command to all slaves

bb+C+A+W/r+Bytes(3)

bb= 11 ssssss is slave address for selection bb-= 01 NA

C=1: following byte is command

A=1: following 2 bytes is address H,L

W/r= 1/0: Write or read cycle w.r.t

Master

Bytes (3): =7: following byte represents

Data size in bytes

=0 to 6 represents no. of data

follows

If write, checksum will be send at end of data and check for Success or error received

if Read, check sum will be send before data and

Data bytes & crieck sum is read

Success or Fail will be acknowledged

Interface signals between Master and Slave

- MOSI

- MISO(slave controlled, Wire ANDed and enabled when needed)

- CLK Typical speed is 100KHz to 1MHz

- nSS invokes interrupt in slave on -ve edge

- •nBSY used for Byte transfer handshake when nSS is active and when nSS is inactive, nBSY pulse from slave may be used to alert master

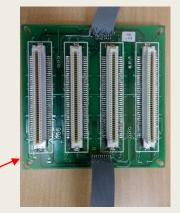

### **Cluster Digitizer Module (CDM)**

### DRS based Digitizer Board (DDB)

#### Header

H10: AN1-8

H28x2: Pixel TRG(4)

Final TRIG

CSTOP

COMSerLink-LVDS

CSPI(5)

10MHz-LVDS

ReqToSend

Flush a Packet

ReadyForTRIG

EN1-8

Flush Over

SerLinkLVDS

MuxedTRG-L

#### DRS Data Packet format (32bit word)

- 0+SFD(15)=0x7BDA+Packet Size(16)

Packet size= Pre(8W)+Pixel Data(variable)+Post(3W)

Pixel data =1W + [ROI/2]xNo. Of valid chnls in a DRS

- Compliment word of first except 1<sup>st</sup> bit

- 0+Event Flags(5) + NU(10)+calibration details(16)

- 0+Event number(31)

- 010+Time stamp in 0.1 usec(29)

- 011+Time stamp in Years(4)+Seconds(25)

- Ob+CDM Position ID(6)+DDB position ID(2)+ DRS temperature(23)

- 0+VCF(9) + LGHG Latch status(8)+CSTOP delay(10)

- {0+Chl ID(4) + STOP cell[10]+skip cells(8)+ROI(9) [0+0+BBD ID(2) + Data(14)+Data(14)]xROI(even)%2

} x Corresponding VCF(9) bits set

- Charge Data for 8 channel (8W=sum of ROI)

- 0+Checksum (2s compl)

- 1+Reserved for packet number by DC 26

- 1+EFD(15) =0x6DAC+ observed Packet size (counter)

### Data Concentrator Module (DCM)

# **Current Status of Back end**

DDB MAX10FPGA Development Board

- CDM board started assembly

- DDB board Assembled and being tested

- DCM concept is tested using two Max10 FPGA-Zest ETM development boards

- Data through-put of 80MBPS is achieved

- CTM NIOS interface to remote PC is tested using Max10 FPGA-Zest ETM development board

- 6 slots prototype of Back panel PCB layout is getting ready

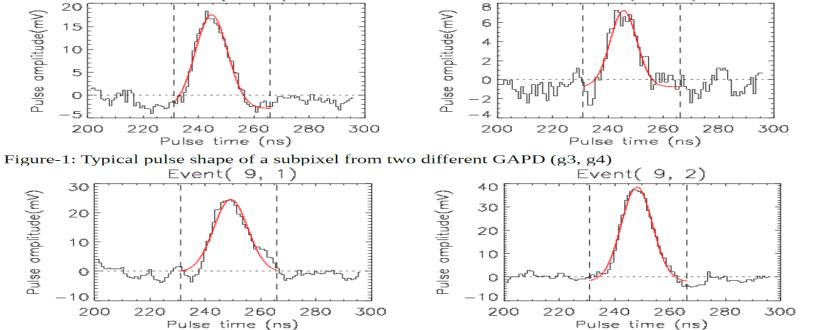

**Figure 1.** (Left panel) Plots of dark count rate versus temperature for several values of overvoltage. (Right panel) Plots of dark count rate versus overvoltage at several temperatures. Both figures are from Vacheret et al. (2011) for Hamamatsu S10362-11-050C.

**Figure 2.** (Left panel) Dark count rate density versus relative overvoltage ( $\Delta V/V_{BD}$ ) for several temperatures. The arrow on the X-axis points to the recommended setting of relative overvoltage. (Right panel) Dark count rate relative to that at 40 °C as a function of temperature at fixed relative overvoltage for Hamamatsu S13360-3050CS SiPM. Source: Otte at al. (2016).

Event( 6, 4)

#### Summary of Test runs taken on 04-April 2018

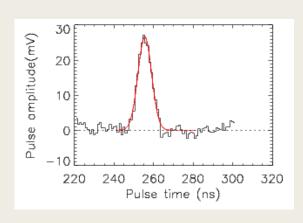

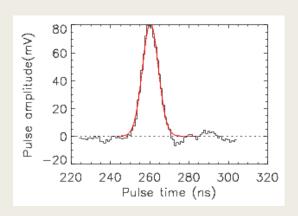

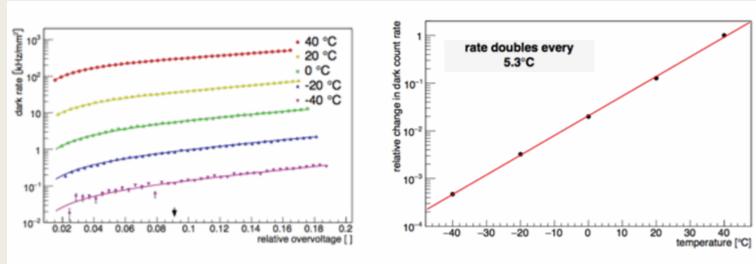

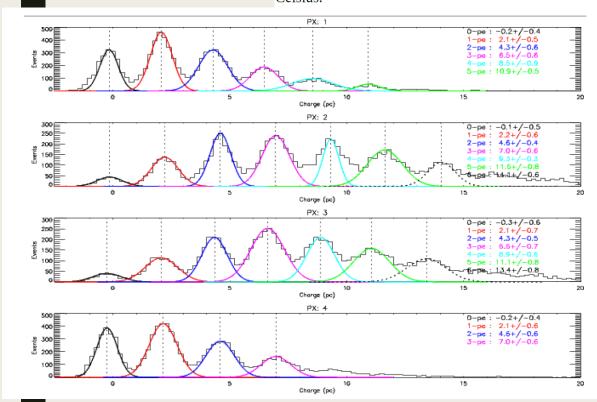

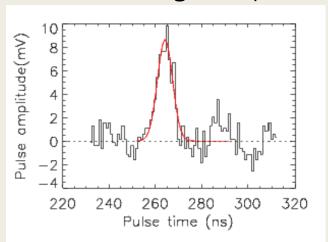

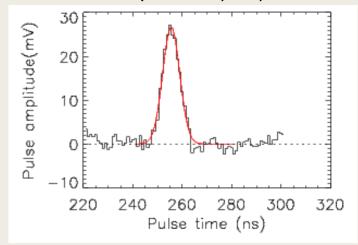

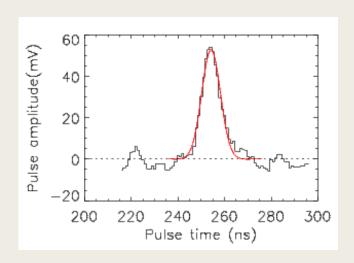

4-GAPDs (pixels) of Pixel Cluster Module (PCM) have been tested along with the cluster digitizer module (CDM). The low/high gain signal (negative pulse) was set as input to CDM unit which gives positive pulse. These pulses were connected directly to VME digitizer setup through 2.5 meters RG174 coaxial cables. The GAPD were operated at 55.0V and temperature was between 24 - 25 degree Celsius.

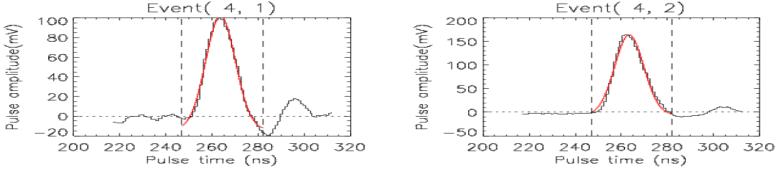

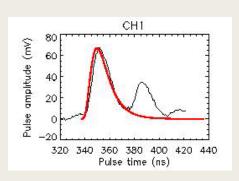

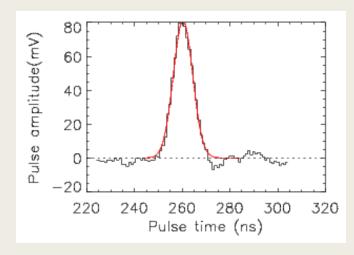

Figure-2: Typical pulse shape of 4-subpixels (added) from two different GAPD (g1, g2)

Event( 6, 3)

Figure-3: Typical pulse shape of 16-subpixels (added) from two different GAPD (g1, g2)

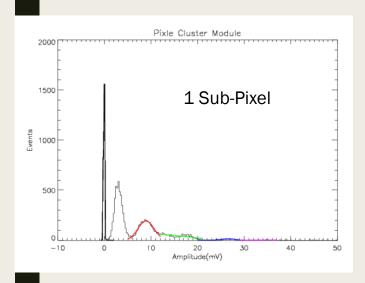

Figure-4: Pulse amplitude and charge distribution of a subpixel (configured as a1). PX1, PX2, PX3 and PX4 refer to four GAPDs (g1,g2,g3,g4) used in PCM.

Figure-5: Pulse amplitude and charge distribution of a subpixel (configured as b2). PX1, PX2, PX3 and PX4 refer to four GAPDs (g1,g2,g3,g4) used in PCM.

Figure-6: Pulse amplitude and charge distribution of a subpixel (configured as c3). PX1, PX2, PX3 and PX4 refer to four GAPDs (g1,g2,g3,g4) used in PCM.

Figure-7: Pulse charge distribution of 4-subpixels (added) (configured as 0660 upper panel and 1248 lower panel). PX1, PX2, PX3 and PX4 refer to four GAPDs (g1,g2,g3,g4) used in PCM.

4-GAPDs (pixels) of Pixel Cluster Module (PCM) have been tested along with the cluster digitizer module (CDM). The low/high gain signal (negative pulse) was set as input to CDM unit which gives positive pulse. These pulses were connected directly to VME digitizer setup through 2.5 meters RG174 coaxial cables. The GAPD were operated at 55.0V and temperature was between 24 - 25 degree Celsius.

#### Summary:

- (a) Pulse shape of subpixels and added subpixels can be fitted with Gaussian function.

- (b) Region of interest (ROI) of 35 ns width with respect to the standard trigger/reference pulse was used to extract amplitude and charge of photoelectrons.

- (c) Mean amplitude of pedestal triggers (zero photoelectron) deviates from zero (positive shifted). In case of charge distribution mean pedestal triggers show close to zero value. The mean pedestal value of amplitude or charge measurement must be zero in the absence of light photons (LED off, GAPD Biased below breakdown voltage).

- (d) Photoelectron peaks of charge distributions are better than corresponding amplitude distribution.

- (e) There is slight variation in the sub-pixel response within a GAPD pixel.

- (f) The gain of PX-2 (g2) is slightly higher than others. This could be due to either GAPD characteristic or pixel-chain.

- (g) In case of 4-subpixels added response no clear separation between photoelectron peaks of amplitude distribution while charge distribution show clear separation.

- (h) In case of of 16-subpixel added response no clear separation between photoelectron peaks of amplitude and charge distribution.

### **Cost Estimation**

1. Cost Amplifier card x 4no.... 18400 (7000 reduction) x4

■ Bias card x 2no ..... 50000 (HV80=45K) x2

■ ......... 15000 (LT3482)x2

Power supply card .... 3000

■ GAPD card ........... 8000(2000 Assembly)

\_\_\_\_\_

- Pixel Cluster Module 184600 ie 11538 per pixel

- \_\_\_\_\_

- 2. Cluster Digitizer Module

- DDB ..... X 4 21000x4

- CDM ..... 5000

- \_\_\_\_\_

- Total........... 89000 ie 5562/pixel

- 3. Other Modules

- CTM ... 15000

- DCM ..... 20000

- 4. Power supply + crate .. 50000 + 250000

- Total cost of DAQ Electronics excluding sensor ..... 47,12,300 or 35,92,600

Cost per pixel is 18400 (17000) or 14000(12600)

# Software

- 1. BIAS firmware:

- Firmware Initialization

- Channel Calibration constants (DAC & ADC), Board ID

- Pixel configuration Data (8 Pixels) from Bias Server

- Temp- coeff , current coeff, Gain-over voltage constants

- Bias parameters Voltage Range, Current limit, Temp range etc

- Temperature and current compensation Loop

- Monitoring (8 pixels)

- Bias voltage, current, GAPD Temp, Bias Temp

- Response to Bias Server commands

- Run control data

- Pixel Bias ON/OFF, Sub pixel ON/OFF

- Required gain

# Software

#### 2. Data Server

There will be two independent event data servers which is receiving event data packets from two Data concentrators in DCM over ethernet and storing in two Data Buffers. These buffers are shared by the event builder

#### 3. Event Builder:

Collate data packets from data servers buffer using linked list buffer with N events(based on event no or time). Write data into event file.

#### 4. Main Console

It is the main Run Console with error window, command buttons

#### 5. Command Server

Commands received from Main console is formatted suitably in packet and send to CTM router

#### 6. Monitor Data Server:

The monitoring Data packets received from CTM router is collated and stored in monitoring file.

#### 7. CTM router

- It is an interface between CTM and Command & Monitoring servers. It suitably packs data compatible to CTM with proper protocol for data transfer.

- 8. Event Monitor Data Analysis with proper displays as well as option of selections.

- Online Analysis is done on both the files and displayed GUI based results. User can also execute specific jobs as when necessary

# Charge

# Camera Electronics

### Camera Electronics components

- Camera Electronics front end

- Pixels Cluster Module -16no.s

- GAPD PCB

- Pre-Amplifier Card 4no.s

- Bias Supply-2no.s

- LV Supply

- Back end Processing & Data Acquisition

- 16 Cluster Digitizer Module 16nos.

- DRS Digitizer Board(DDB) 4no.s in each CDM

- Data Concentrator Module- 1no.

- Trigger & Control Module -1no.

- Bias Server -1 no.

### 1 Sub Pixel Addition after

Juli Ividy, ZUIU

Amplitude (mV)

esh S Upadhya , TIFR, Mumbai

Peak time (ns)

### Characterization of Hamamatsu S13361-3050AS-04

# Pixel Cluster Module

# G-APD Pulses of High Gain Channel

### Single sub-pixel enabled in a Pixel Amplifier 1/10/18

4 Pixels Amplifier card

### All 16 sub-pixels enabled in a Pixel Amplifier

Amplifier with test ZIG & CDM